Multicomputer software development systems come of age

StoryApril 02, 2008

It was not so long ago that the typical DSP development package was a set of optimized libraries, plus a port to the industry standard Vector Signal Image Processing Library (VSIPL) and a driver for an RTOS. While these are still essential elements for algorithm development, the platforms that host DSP applications have become much more complex.

It was not so long ago that the typical DSP development package was a set of optimized libraries, plus a port to the industry standard Vector Signal Image Processing Library (VSIPL) and a driver for an RTOS. While these are still essential elements for algorithm development, the platforms that host DSP applications have become much more complex, offering FPGA front ends and multicompute engines for DSP and general purpose processors for back-end interfacing to displays and data processing systems. The tools required to visualize, model, program, and debug these systems have also become more complex, supporting a wide variety of hardware architectures and configurations.

Visualization and modeling

Creating a complete, dynamic model of the system to be implemented, tested, and validated is a vital part of the design and development process. In the large majority of military DSP applications, it is unlikely that a single processor would have the capacity to resolve the problem alone. It needs to be broken down into smaller tasks, data flows, and processing capacity and then mapped onto available hardware capability. Thus, COTS vendors now offer the tools to describe and visualize this design process from the creation of a task structure to the hardware features of their products. These might include number and type of processors per module, memory capacity and bandwidth, interconnect type and bandwidth between processors, plus interconnects between modules using fabrics. By understanding the relationship between these features and the system's performance requirements, decisions can be made on how the application is constructed and distributed across multiple modules and processing nodes.

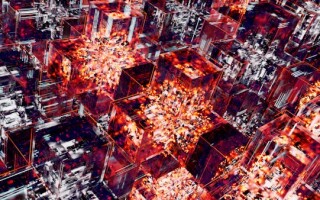

The same models translate into the test and verification of a real system. Tools are used to verify hardware configuration, to download and test selected parts of the application, and to analyze and debug the behavior of multiple processing nodes in real time. Accurately time-stamped data is collected by lightweight instrumentation to display data flows, processing times, and events – and to compare them with predicted values generated during the design process. Figure 1 illustrates a typical display of task, processor, and fabric activity captured by GE Fanuc Intelligent Platforms' AXIS integrated development environment, which supports the complete development cycle of these complex multicomputing systems.

Figure 1

Communications

COTS vendors have created scalable multicomputing architectures to deal with the complexity of many military DSP applications. These require large numbers of compute nodes and high-bandwidth data paths to communicate between them. This complexity impacts the application developer in two ways. First, it requires a communications infrastructure to be developed between nodes and across fabrics. Second, it requires constant maintenance and support if hardware devices or fabric types were to change, which is natural as COTS hardware platforms evolve.

While current generations of hardware use PCI-similar fabrics such as StarFabric, new standards point to the widespread adoption of Serial RapidIO, PCIe, and 10 GbE for these multicomputer fabrics. To preempt these changes and make their products easier to use, COTS vendors are offering feature-rich interprocessor communications APIs that will remain constant, whatever the fabric's hardware implementation. This abstraction will also extend to RTOSs as the API grows to encompass the broader range of calls used to implement a DSP application, offering an almost transparent choice of RTOS, fabric, and processor to the user.

DSP libraries

Military applications generally use floating point math for accuracy and speed. Accordingly, the popular choice is Freescale Semiconductor's Power Architecture processor with AltiVec or specialized DSP processing devices such as Analog Devices' TigerSHARC. Power Architecture offers the advantage that processing nodes can also be used more easily for general purpose processing and management tasks to maintain a common hardware and development tool base across an entire system development. DSP function libraries for the respective processor types, often optimized by the module vendor, complete the development toolset, allowing the user to extract maximum performance from a specific hardware implementation.

While the DSP library is undoubtedly a vital element in DSP algorithm development, its impact on the overall development cost, timescales, and through-life sustainment costs of a complex new multicomputing development project is overshadowed by the broader toolsets now offered by hardware vendors. Modeling, visualization, verification, and abstraction tools are all good indications of the newfound maturity of the technology and its success in the future.

To learn more, e-mail Duncan Young at